#### FIELD OF SCIENCE ENGINEERING AND TECHNOLOGY

SCIENTIFIC DISCIPLINE AUTOMATICS ELECTRONICS, ELECTRICAL ENGINEERING AND SPACE TECHNOLOGY

## **DOCTORAL DISSERTATION**

Pixel Radiation Detectors with in-situ Signal Processing, and Event-Triggered, Throughput-Optimized Readout Methods

Author: mgr inż. Dominik Górni

Supervisor: prof. Grzegorz Deptuch, PhD, DSc

Completed at: AGH University of Krakow, Faculty of Electrical Engineering, Automatics, Computer Science and Biomedical Engineering

AKADEMIA GÓRNICZO-HUTNICZA IM. STANISŁAWA STASZICA W KRAKOWIE

#### DZIEDZINA NAUK INŻYNIERYJNO-TECHNICZNYCH

DYSCYPLINA AUTOMATYKA, ELEKTRONIKA, ELEKTROTECHNIKA I TECHNOLOGIE KOSMICZNE

### ROZPRAWA DOKTORSKA

Pikselowe detektory promieniowania z in-situ przetwarzaniem sygnałów, i z wyzwalanymi zdarzeniami, zoptymalizowanymi pod kątem przepustowości sposobami odczytu

Autor: mgr inż. Dominik Górni

Promotor rozprawy: prof. dr hab. inż. Grzegorz Deptuch

Praca wykonana: AGH Akademia Górniczo-Hutnicza, Wydział Elektrotechniki, Automatyki, Informatyki i Inżynierii Biomedycznej

I owe my deepest gratitude to my supervisor, whose scholarly insight, substantive guidance, and high standards shaped this dissertation at every stage. His questions sharpened my arguments, his comments improved the clarity, and his example set the tone for rigor and curiosity. Thank you for the time, patience, and trust you invested in me.

I am equally grateful to the staff of Brookhaven National Laboratory (BNL). Your support, ranging from access to facilities and tools to countless technical discussions and everyday help with logistics, made this work possible. The generosity with which you shared expertise and solved problems alongside me will remain a model of collaboration.

To my friend Piotr – thank you for keeping me moving when momentum faltered: for the checkins, and the steady belief that this could be finished well.

To my parents, thank you for your unwavering love, patience, and encouragement.

Finally, to all colleagues, mentors, reviewers, lab technicians, administrators, and friends whose names I cannot list individually but whose contributions mattered: thank you. Any remaining errors are mine alone.

## **Abstract**

Modern pixel radiation detectors face a persistent readout bottleneck: as pixel counts and event rates increase, conventional frame-based and polling-based schemes waste bandwidth, induce latency, and can bias acquisition due to fixed priorities. This dissertation addressed the problem by proposing, implementing, and validating a new event-driven readout architecture that combined in-situ signal processing with asynchronous, non-priority arbitration to deliver low latency, optimized throughput, and fair data transfer from large pixel matrices. The central hypothesis stated that the novel readout architecture features near-ideal event-driven operation and asynchronous arbitration logic with non-priority access, implemented as a tree of RS-latch-based arbiters, will provide significant improvements for high-density pixel radiation detectors by achieving higher throughput, lower latency, and demonstrably fairer event handling compared to traditional frame-based, polling-based, and priority-encoded readout architectures, thus enabling a new generation of pixel detectors.

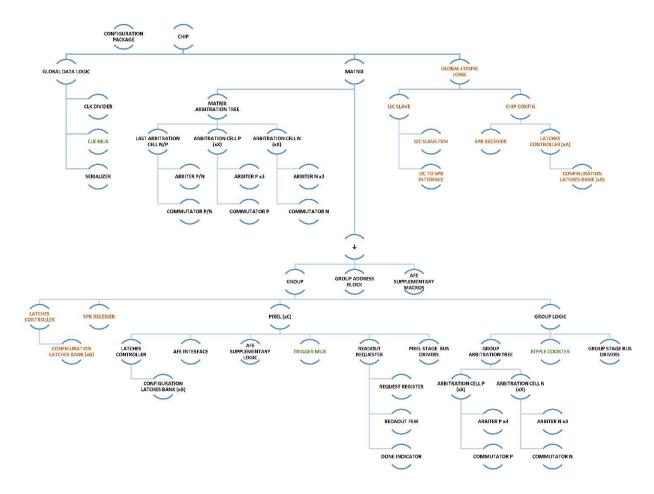

The proposed system, named **EDWARD** (Event Driven With Access and Reset Decoder), initiates data movement only when a meaningful event occurs in a pixel. EDWARD employs request/acknowledge handshakes, a non-priority tree of RS-latch-based arbiters, and a multi-phase transaction that can transmits address, timestamp, amplitude, and other data without collisions. In contrast to prior-art Address Event Representation (AER) and snapshot-based Address-Encoder and Reset-Decoder (AERD) schemes, EDWARD guarantees transactional completion and fairness through arbiters with memory elements and does not require periodic snapshot strobes. This eliminates the dead time and the risks of stuck handshakes and priority bias while preserving sparse, event-only traffic.

One of the key architectural contribution lie in the bridge between asynchronous pixels and synchronous data acquisition: acknowledge signal is generated in a form of a *tokens* in the periphery, aligned to a serializer clock, and routed by the arbitration tree only toward active requesting channels (pixels). Each acknowledge edge advance a pixel's local multi-phase readout; when a transaction finish, the token is immediately eligible for reuse. This design preserve the benefits of asynchronous, self-timed logic inside the matrix while exposing a clean, clocked interface at the output.

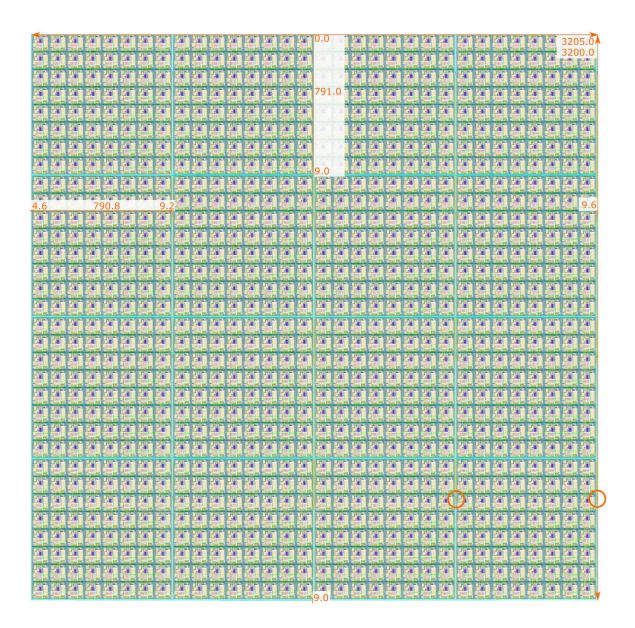

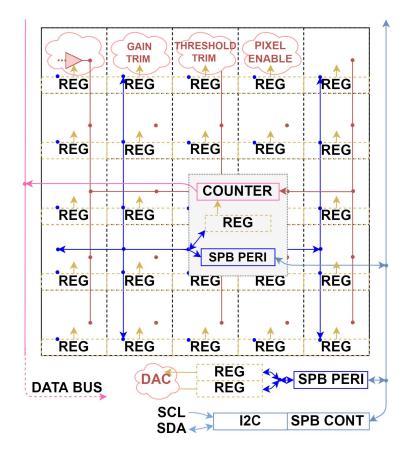

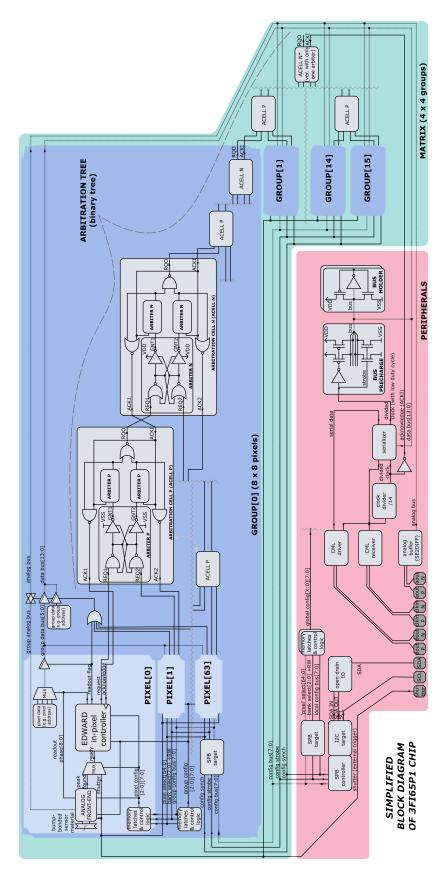

Two silicon prototypes were realized and tested to validate the concept. The **3FI65P1** chip integrated a  $32 \times 32$  matrix (100  $\mu$ m pitch) with a complete analog front end for spectroscopic imaging (X-ray fluorescence), asynchronous EDWARD logic, configuration/testability, and high-speed serialization. The author implemented the asynchronous digital logic and the configuration-testability-readout (CTR) platform. The analog front end and periphery were developed in collaboration with the Brookhaven National Laboratory (BNL) ASIC Team.

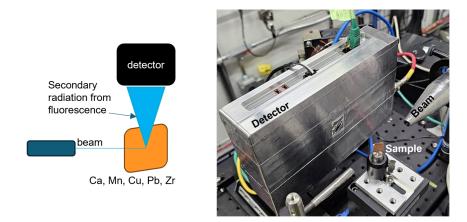

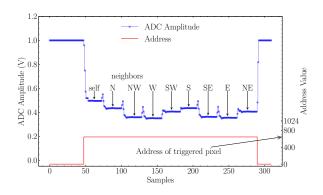

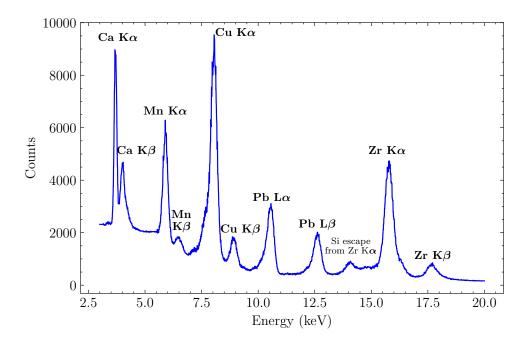

The mixed-signal 3FI65P1 prototype demonstrates EDWARD in practical detector modes. A single pixel (throughput-optimized) mode transmits the addressed pixel's amplitude; a charge sharing compensation (energy-optimized) mode performs a nine-phase readout, including data from neighbor pixels, that preserves bus ownership across phases, verified by one-to-one correlation between the analog sample-and-hold waveform and the serialized address stream. These experiments confirmed correct multi-phase handshaking and bus exclusivity with no spurious samples. In preliminary synchrotron tests at NSLS-II (beamline 17-BM), 3FI65P1 delivered 138 eV FWHM at Ca K $\alpha$  and 308 eV FWHM at Cu K $\alpha$  over a 2.5–20 keV window, demonstrating that the in-situ processing plus event-driven readout met spectroscopic targets in a high-background environment.

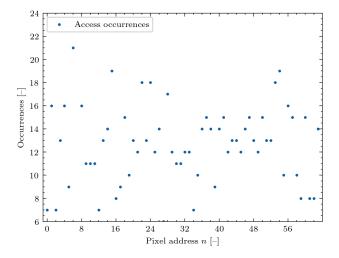

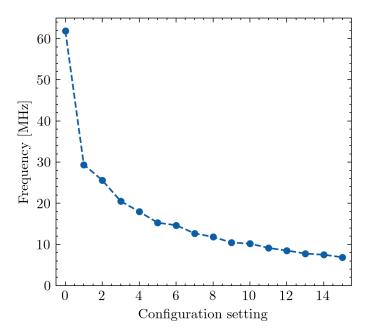

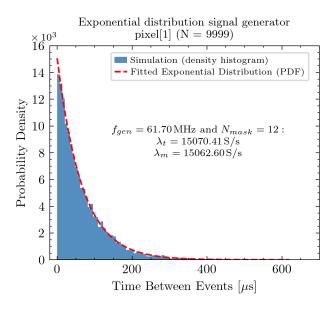

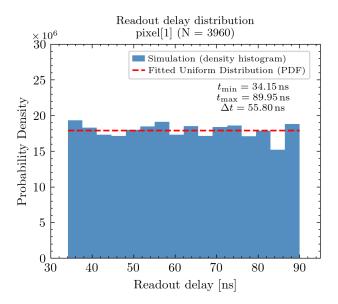

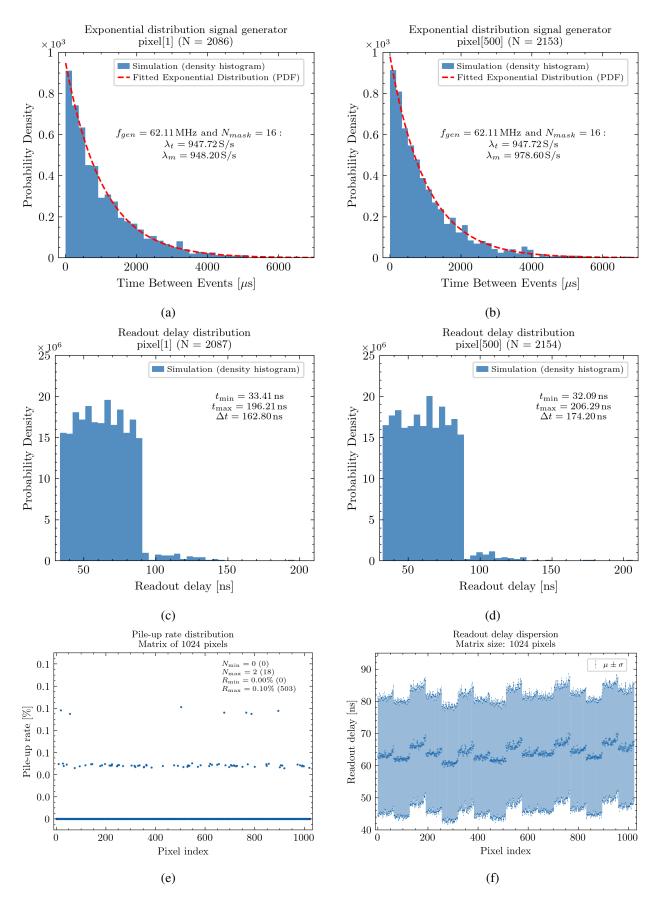

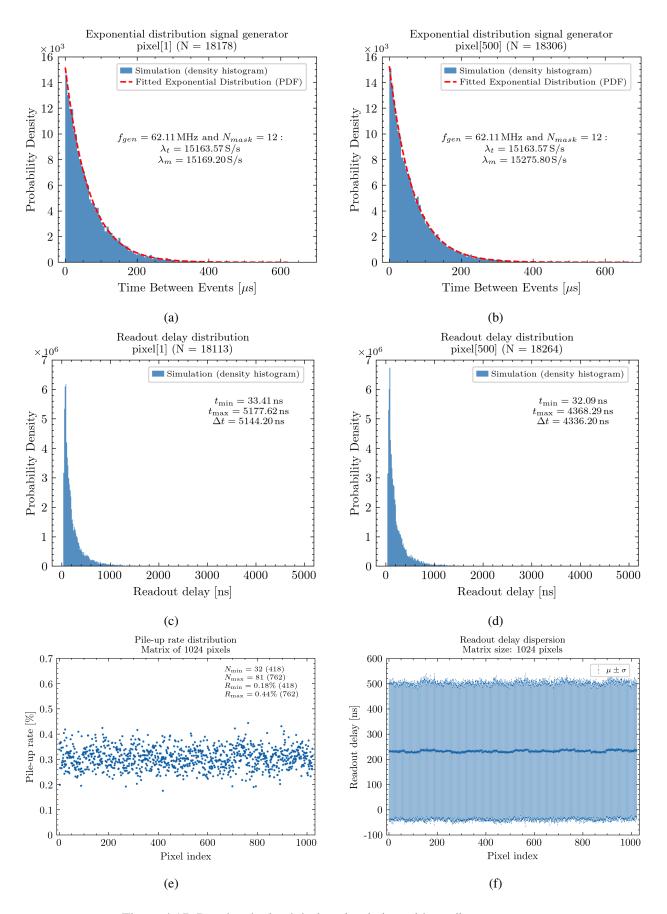

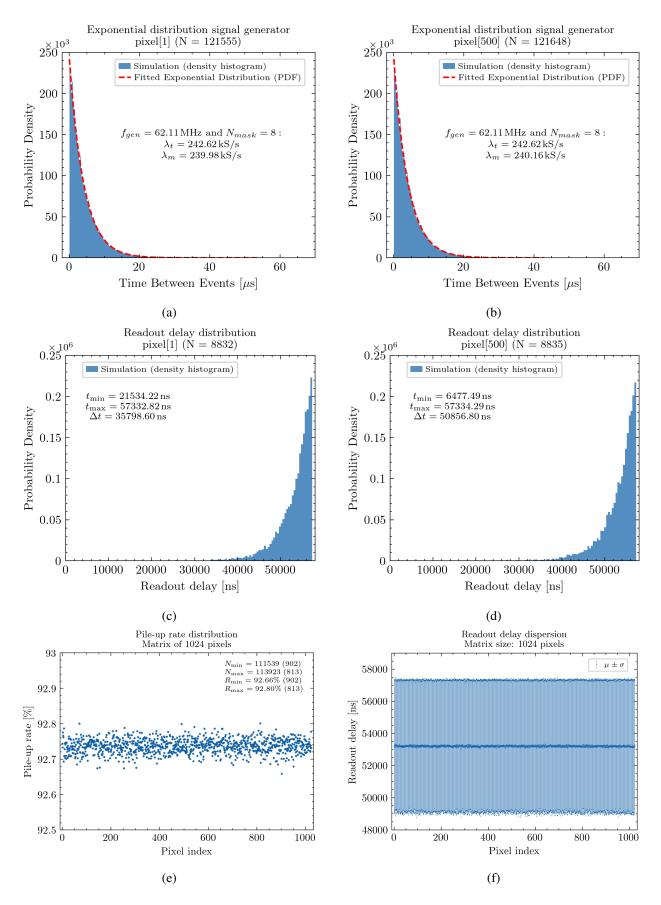

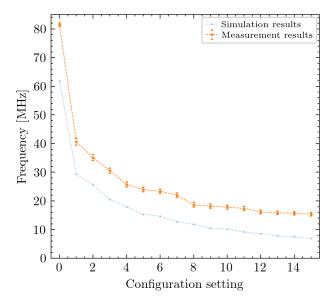

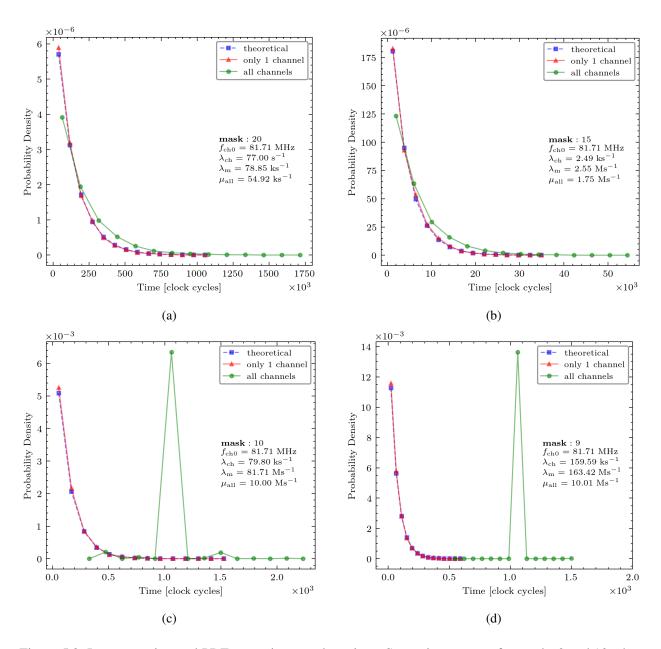

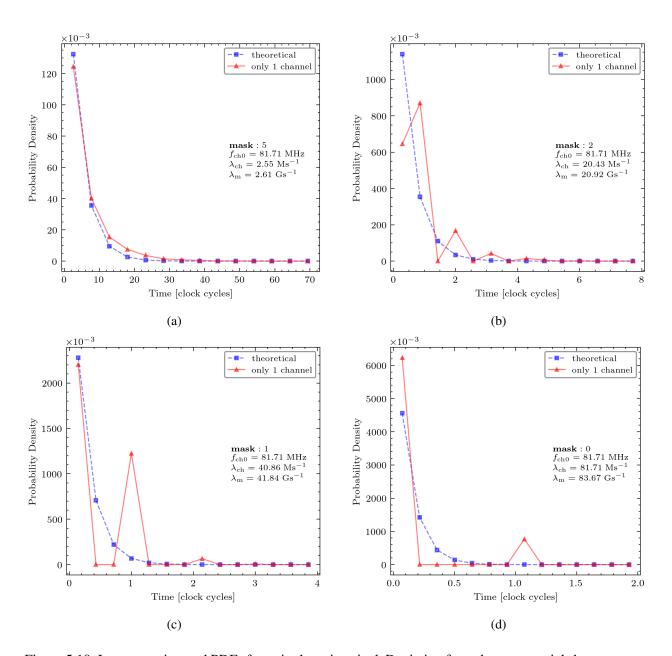

The **EDWARD65P1** chip, a digital-only derivative with identical arbitration/serialization but in-pixel programmable event generators, enables controlled, matrix-wide stress tests to quantify latency, throughput, fairness, and token reuse behavior independently of analog effects. The validation employed a combination of simulation (digital and mixed-signal), queuing model analysis, and measurements on fabricated ASICs. An M/G/1/N queuing model captured arrival and service statistics in the serialized output path and guided the interpretation of latency and pile-up under increasing load. In EDWARD65P1 simulations and measurements, the in-pixel Poisson generator reproduced the expected exponential inter-arrival distribution with high fidelity (e.g., measured  $\lambda=15,062.6~\rm s^{-1}$  versus a theoretical rate of 15,070.4 s<sup>-1</sup>), confirming a realistic traffic source for matrix testing.

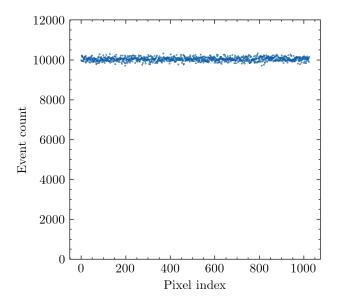

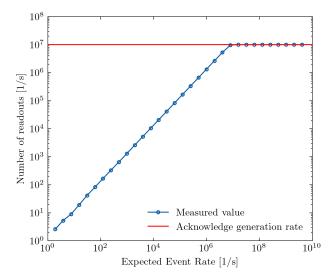

Performance results supported the hypothesis. Under moderate load, the architecture achieved sub-microsecond average access times while avoiding the matrix-size latency growth typically associated with prioritized or scanned designs. Throughput approached the theoretical acknowledge frequency ceiling, on the order of 10–17 MHz, depending on the serializer speed, because only active pixels engaged the bus, and token reuse eliminated enforced idle cycles. Measured saturation in EDWARD65P1 occurred near the 10 MHz acknowledge limit, in line with the analysis. Arbitration remained uniform and starvation-free across the matrix, with no spatial bias even for bursty Poisson traffic.

Across studies, EDWARD reduced redundant transfers relative to frame readout, avoided polling latency, and minimized dynamic power by remaining quiescent in the absence of events – features especially valuable for sensitive analog front ends. Fair, non-priority arbitration eliminated deterministic bias and protected data integrity without combinational conflicts. Together, these traits improved time resolution, reduced pile-up, and enabled larger arrays or higher frame-equivalent rates without requiring additional Input/Output ports.

Original contributions include: (i) the EDWARD architecture – a fully asynchronous, non-priority, event-driven pixel readout with RS-latch-based arbiters and multi-phase transactions; (ii) tight integration of in-situ signal processing with event-triggered digital transport; (iii) practical asynchronous-to-synchronous interfacing (tokenized acknowledge and serializer alignment) within standard flows; (iv) hardware prototyping in 65 nm CMOS (3FI65P1 and EDWARD65P1) with empirical evidence of fairness, latency, and bandwidth gains; and (v) a modular platform for configuration, testability, and readout control.

The work also documents practical design compromises. Asynchronous arbiters were integrated into an otherwise conventional RTL-to-GDSII flow by introducing custom cells, excluding them from static timing

analysis, and relying on focused verification and mixed-mode simulation to ensure glitch-free operation. These accommodations do not pose fundamental barriers to scaling or porting to advanced nodes.

Finally, the dissertation outlines scalability paths, including hierarchical trees, subarray partitioning, and multi-bus topologies, to reduce worst-case propagation and enable parallel outputs for large matrices. These options trade silicon area for reduced arbitration depth and higher aggregate bandwidth, offering design freedom for detector-specific constraints.

In summary, by re-examining the fundamental principles of pixel readout and demonstrating a fair, asynchronous, event-triggered alternative in silicon, this work advances the state of the art in radiation detector instrumentation. The demonstrated gains in latency, throughput, and energy efficiency, together with robust asynchronous-to-synchronous interfacing, make the approach attractive for next-generation X-ray imaging, particle tracking at high-luminosity colliders, and other experiments that demand fast, unbiased, and bandwidth-efficient detection.

## Streszczenie

Nowoczesne pikselowe detektory promieniowania zmagają się z utrzymującym się wąskim gardłem odczytu: wraz ze wzrostem liczby pikseli i częstości zdarzeń konwencjonalne schematy oparte na odczycie ramkowym i sondowaniu marnują pasmo, wprowadzają opóźnienia i mogą powodować stronniczość akwizycji z powodu stałych priorytetów. Niniejsza rozprawa rozwiązała ten problem poprzez zaproponowanie, implementację i weryfikację nowej, zdarzeniowej architektury odczytu, łączącej przetwarzanie sygnału in-situ z asynchronicznym, nie priorytetowym arbitrażem w celu zapewnienia niskich opóźnień, zoptymalizowanej przepustowości oraz sprawiedliwego transferu danych z dużych matryc pikseli. Główna hipoteza zakładała, że nowa architektura odczytu, charakteryzująca się niemal idealną pracą zdarzeniową oraz asynchroniczną logiką arbitrażu z dostępem bez priorytetów, zaimplementowaną jako drzewo arbitrów opartych na zatrzaskach RS, zapewni istotną poprawę dla gęstych detektorów pikselowych promieniowania, osiągając wyższą przepustowość, niższe opóźnienia i wykazalnie sprawiedliwszą obsługę zdarzeń w porównaniu z tradycyjnymi architekturami odczytu ramkowymi, opartymi na sondowaniu i z kodowaniem priorytetów, umożliwiając tym samym nową generację detektorów pikselowych.

Proponowany system, nazwany **EDWARD** (ang. Event Driven With Access and Reset Decoder), inicjuje przepływ danych tylko wtedy, gdy w pikselu wystąpi istotne zdarzenie. EDWARD wykorzystuje uzgodnienia (ang. handshakes) typu żądanie/potwierdzenie, nie priorytetowe drzewo arbitrów opartych na zatrzaskach RS oraz wielofazową transakcję, która może przekazywać adres, znacznik czasu, amplitudę i inne dane bez kolizji. W przeciwieństwie do Address Event Representation (AER) i migawkowych schematów Address-Encoder and Reset-Decoder (AERD) znanych z literatury, EDWARD gwarantuje domknięcie transakcyjne i sprawiedliwość dzięki arbitrom z elementami pamięci i nie wymaga okresowych sygnałów strobujących. Eliminuje to martwy czas oraz ryzyko zawieszających się uzgodnień i uprzedzeń priorytetowych, przy jednoczesnym zachowaniu rzadkiego, wyłącznie zdarzeniowego ruchu.

Jednym z kluczowych wkładów architektonicznych jest pomost między asynchronicznymi pikselami a synchroniczną akwizycją danych: sygnał potwierdzenia jest generowany w peryferiach w postaci *żetonów* (ang. token), zsynchronizowanych do zegara serializera i kierowanych przez drzewo arbitrażu jedynie do aktywnie żądających kanałów (pikseli). Każde zbocze potwierdzenia przesuwa lokalny, wielofazowy odczyt piksela; gdy transakcja się kończy, żeton jest natychmiast gotów do ponownego użycia. Ten projekt zachowuje zalety asynchronicznej, samotaktującej się logiki wewnątrz matrycy, jednocześnie udostępniając czysty, zegarowy interfejs na wyjściu.

Zrealizowano i przetestowano dwa prototypy wykonane w technologii krzemowej w celu weryfikacji koncepcji. Układ **3FI65P1** integrował matrycę  $32 \times 32$  (rozstaw 100  $\mu$ m) z kompletnym anal-

ogowym torem wejściowym (ang. analog front-end) do obrazowania spektroskopowego (fluorescencja rentgenowska), asynchroniczną logiką EDWARD, mechanizmami konfiguracji/testowalności oraz szybką konwersję równoległo-szeregową (ang. high-speed serialization). Autor zaimplementował asynchroniczną logikę cyfrową oraz platformę konfiguracji–testowalności–odczytu (CTR). Analogowy tor wejściowy i peryferia opracowano we współpracy z zespołem ASIC Brookhaven National Laboratory (BNL).

Prototyp mieszany 3FI65P1 demonstruje EDWARD w praktycznych trybach pracy detektora. Tryb pojedynczego piksela (zoptymalizowany pod kątem przepustowości) przesyła amplitudę adresowanego piksela; tryb kompensacji dzielenia ładunku (zoptymalizowany pod kątem energii) realizuje dziewięciofazowy odczyt, obejmujący dane z pikseli sąsiednich, który utrzymuje własność magistrali między fazami, co zweryfikowano poprzez korelację jeden-do-jeden między analogowym przebiegiem z układu próbkującego a strumieniem danych w postaci adresów. Eksperymenty te potwierdziły poprawny wielofazowe uzgodnienia i wyłączność magistrali bez fałszywych próbek. We wstępnych testach na synchrotronie NSLS-II (linia 17-BM) 3FI65P1 osiągnął 138 eV FWHM dla Ca K $\alpha$  oraz 308 eV FWHM dla Cu K $\alpha$  w oknie 2.5–20 keV, pokazując, że przetwarzanie in-situ wraz ze zdarzeniowym odczytem spełniły cele spektroskopowe w środowisku o wysokim tle.

Układ **EDWARD65P1**, cyfrowa pochodna z identycznym arbitrażem/konwersją równoległo-szeregową, lecz z programowalnymi w pikselu generatorami zdarzeń, umożliwia kontrolowane, obejmujące całą matrycę testy przeciążeniowe w celu ilościowego określenia opóźnień, przepustowości, sprawiedliwości i zachowania ponownego użycia żetonów, niezależnie od efektów analogowych. Walidacja wykorzystywała kombinację symulacji (cyfrowych i mieszanych), analizy modelu kolejkowego oraz pomiarów na wytworzonych układach ASIC. Model kolejkowy M/G/1/N opisywał statystyki przyjść i obsługi w ścieżce wyjściowej i kierował interpretacją opóźnień oraz nakładania się zdarzeń (ang. pile-up) przy rosnącym obciążeniu. W symulacjach i pomiarach EDWARD65P1, generator Poissona w pikselu odtworzył oczekiwany wykładniczy rozkład czasów międzyprzyjściowych z wysoką wiernością (np. zmierzone  $\lambda=15062, 6~\rm s^{-1}$  wobec teoretycznej wartości  $15070, 4~\rm s^{-1}$ ), potwierdzając realistyczne źródło ruchu do testowania matrycy.

Wyniki wydajnościowe potwierdziły hipotezę. Przy umiarkowanym obciążeniu architektura osiągała średnie czasy dostępu poniżej mikrosekundy, unikając wzrostu opóźnień zależnego od rozmiaru matrycy, typowego dla konstrukcji z priorytetami lub skanowaniem. Przepustowość zbliżała się do teoretycznego pułapu częstotliwości potwierdzeń, rzędu 10–17 MHz, w zależności od szybkości konwersji równoległoszeregowej, ponieważ tylko aktywne piksele zajmowały magistralę, a ponowne użycie żetonów eliminowało wymuszone cykle bezczynności. Zmierzona saturacja w EDWARD65P1 wystąpiła w pobliżu limitu potwierdzeń 10 MHz, zgodnie z analizą. Arbitraż pozostawał jednolity i wolny od zagłodzenia w całej matrycy, bez przestrzennej stronniczości, nawet dla impulsowego charakteru procesu Poissona.

W przekroju badań EDWARD redukował redundantne transfery względem odczytu ramkowego, unikał opóźnień sondowania i minimalizował moc dynamiczną, pozostając w stanie spoczynku przy braku zdarzeń – cechy szczególnie cenne dla czułych analogowych front-endów. Sprawiedliwy, nie priorytetowy arbitraż eliminował deterministyczną stronniczość i chronił integralność danych bez konfliktów kombinacyjnych. Łącznie cechy te poprawiały rozdzielczość czasową, redukowały pile-up i umożliwiały większe matryce

lub wyższe równoważne częstotliwości ramkowe bez konieczności dodawania dodatkowych portów wejścia/wyjścia.

Oryginalny wkład pracy obejmuje: (i) architekturę EDWARD – w pełni asynchroniczny, nie priorytetowy, zdarzeniowy odczyt pikseli z arbitrami opartymi na zatrzaskach RS i transakcjami wielofazowymi; (ii) ścisłą integrację przetwarzania in-situ sygnałów z wyzwalanym zdarzeniami odczytem cyfrowym; (iii) praktyczne łączenie asynchroniczno-synchroniczne (tokenizowane potwierdzenie i wyrównanie do serializera) w standardowych ścieżkach projektowania; (iv) prototypowy sprzętowe w technologii 65 nm CMOS (3FI65P1 i EDWARD65P1) z empirycznymi dowodami zysków w zakresie sprawiedliwości, opóźnień i przepustowości; oraz (v) modułową platformę konfiguracji, testowalności i sterowania odczytem.

Praca dokumentuje również praktyczne kompromisy projektowe. Asynchroniczne arbitry włączono do inaczej konwencjonalnego przepływu RTL-do-GDSII poprzez wprowadzenie komórek niestandardowych, wyłączenie ich ze statycznej analizy czasowej oraz oparciu się na ukierunkowanej weryfikacji i symulacji trybu mieszanego w celu zapewnienia pracy wolnej od zakłóceń. Te dostosowania nie stanowią zasadniczych przeszkód dla skalowania ani przenoszenia do zaawansowanych technologii.

Wreszcie, rozprawa zarysowuje ścieżki skalowalności, w tym drzewa hierarchiczne, tworzenie podmacierzy i topologie wielomagistralowe, w celu ograniczenia najgorszego przypadku propagacji i umożliwienia równoległych wyjść dla dużych matryc. Opcje te wymieniają powierzchnię układu krzemowego na mniejszą głębokość arbitrażu i większą łączną przepustowość, oferując swobodę projektową przy specyficznych ograniczeniach detektora.

Podsumowując, ponowne przeanalizowanie podstawowych zasad odczytu pikseli i demonstracja w technologii krzemowej sprawiedliwej, asynchronicznej alternatywy wyzwalanej zdarzeniami dla odczytu przesuwa stan techniki w instrumentacji detektorów promieniowania. Wykazane zyski w zakresie opóźnień, przepustowości i efektywności energetycznej, wraz z odpornym łączeniem asynchroniczno-synchronicznym, czynią to podejście atrakcyjnym dla następnej generacji obrazowania rentgenowskiego, śledzenia cząstek w zderzaczach o wysokiej świetlności oraz innych eksperymentów wymagających szybkiej, bezstronnej i zoptymalizowanej pod kątem przepustowości detekcji.

## **Contents**

| Li                            | st of I | igures   |                                                            | xvii |

|-------------------------------|---------|----------|------------------------------------------------------------|------|

| Li                            | st of A | Abbrevi  | ations                                                     | xxi  |

| 1                             | Intr    | oductio  | on.                                                        | 1    |

| 1.1 Background and Motivation |         |          |                                                            |      |

|                               |         | 1.1.1    | The Expanding Field of Radiation Detector Applications     | . 1  |

|                               |         | 1.1.2    | Pixel Radiation Detectors                                  | . 2  |

|                               |         | 1.1.3    | Challenges and Bottlenecks in Pixel Detector Readout       | . 4  |

|                               | 1.2     | Resea    | arch Problem Statement and Objectives                      | . 5  |

|                               |         | 1.2.1    | Limitations of Existing Readout Architectures              | . 5  |

|                               |         | 1.2.2    | Research Questions and Hypothesis                          | . 7  |

|                               |         | 1.2.3    | Dissertation Objectives Aligned with Research Questions    | . 8  |

|                               | 1.3     | Disse    | rtation Scope                                              | . 9  |

|                               | 1.4     | Disse    | rtation Structure                                          | . 10 |

| 2                             | Lite    | rature ] | Review                                                     | 13   |

|                               | 2.1     | Funda    | amental Principles of Radiation Detectors                  | . 13 |

|                               |         | 2.1.1    | Types of Radiation Detectors                               | . 13 |

|                               |         | 2.1.2    | Radiation Interaction Mechanisms                           | . 16 |

|                               |         | 2.1.3    | Signal Formation in Semiconductor Detectors                | . 18 |

|                               | 2.2     | Solid-   | -State Pixel Detector Types                                | . 19 |

|                               |         | 2.2.1    | Hybrid Pixel Detectors (HPD)                               | . 19 |

|                               |         | 2.2.2    | Monolithic Active Pixel Sensors (MAPS)                     | . 21 |

|                               |         | 2.2.3    | Comparative Summary of Hybrid and Monolithic Architectures | . 24 |

|                               | 2.3     | In-Sit   | tu Signal Processing Techniques                            | . 24 |

|                               |         | 2.3.1    | Motivation for In-Situ Signal Processing                   | . 24 |

|                               |         | 2.3.2    | Established Techniques                                     | . 25 |

|                               |         | 2.3.3    | Detector Operation Modes                                   | . 27 |

|                               |         | 2.3.4    | Noise Considerations                                       | . 28 |

|                               |         | 2.3.5    | Challenges in Implementing In-Situ Processing              | . 29 |

|                               | 2.4     | Tradit   | tional Readout Methods                                     | . 29 |

|                               |         | 2.4.1    | Direct Link Readout Architecture                           | . 29 |

|   |      | 2.4.2  | Frame-Based Readout Architecture                                           | 31 |

|---|------|--------|----------------------------------------------------------------------------|----|

|   |      | 2.4.3  | Polling-Based Readout Architecture: General Concept and Example from VIP2a | 33 |

|   |      | 2.4.4  | Summary of Conventional Readout Architectures                              | 34 |

|   | 2.5  | Asyno  | chronous Logic in Pixel-Detector Readout                                   | 36 |

|   | 2.6  | Asyno  | chronous, Event-Driven Readout Architectures                               | 40 |

|   |      | 2.6.1  | The Address-Event Representation Protocol                                  | 40 |

|   |      | 2.6.2  | Address-Encoder and Reset-Decoder Architecture                             | 42 |

| 3 | Prop | osed E | DWARD Architecture                                                         | 45 |

|   | 3.1  | Archi  | tecture Overview and Design Objectives                                     | 45 |

|   |      | 3.1.1  | Rationale for Event-Driven Approach                                        | 45 |

|   |      | 3.1.2  | Objectives: Throughput Optimization, Latency Minimization, Fairness        | 45 |

|   | 3.2  | EDW    | ARD System-Level Description                                               | 46 |

|   |      | 3.2.1  | Functional Block Diagram                                                   | 46 |

|   | 3.3  | In-Ch  | nannel Logic and Data Handling                                             | 47 |

|   |      | 3.3.1  | Event Detection and Request Generation                                     | 47 |

|   |      | 3.3.2  | Token Concept and Asynchronous Handshake                                   | 47 |

|   |      | 3.3.3  | Multi-Phase Readout and Done Signal                                        | 47 |

|   |      | 3.3.4  | Parallel Digital and Analog Output                                         | 48 |

|   |      | 3.3.5  | Asynchronous Logic and Phase Progression                                   | 48 |

|   |      | 3.3.6  | Channel Configuration and Operational Modes                                | 49 |

|   | 3.4  | Asyno  | chronous Arbitration Mechanism                                             | 50 |

|   |      | 3.4.1  | Seitz Arbiter and Grant Logic                                              | 50 |

|   |      | 3.4.2  | Arbitration Cell Type 0: Baseline Behavior                                 | 51 |

|   |      | 3.4.3  | Arbitration Cell Type II: Framed Request Gating                            | 53 |

|   |      | 3.4.4  | Arbitration Cell Type I: Fairness-Oriented Design                          | 54 |

|   |      | 3.4.5  | Arbitration Tree Organization                                              | 56 |

|   | 3.5  | Synch  | nronization Mechanism and Peripheral Operation                             | 58 |

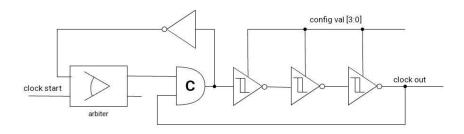

|   |      | 3.5.1  | Global Clock and Acknowledge Token Relationship                            | 61 |

|   |      | 3.5.2  | Token Lifetime and Reuse                                                   | 61 |

|   |      | 3.5.3  | Local vs. Global Synchronization                                           | 61 |

|   |      | 3.5.4  | Valid Data Detection and Idle State Handling                               | 62 |

|   |      | 3.5.5  | Data Serialization and Output Streaming                                    | 62 |

|   |      | 3.5.6  | Architectural Scalability                                                  | 64 |

|   |      | 3.5.7  | Hierarchical Trees and Multi-Bus Topologies                                | 64 |

|   | 3.6  | 3FI65  | SP1 Chip                                                                   | 67 |

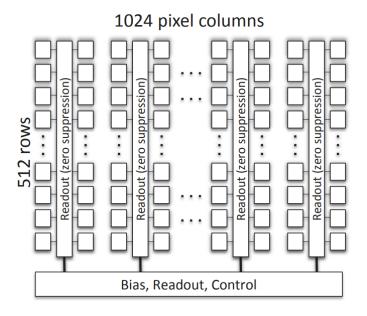

|   |      | 3.6.1  | Physical Structure and Pixel Matrix Organization                           | 67 |

|   |      | 3.6.2  | Analog Front-End Architecture                                              | 69 |

|   |      | 3.6.3  | Implementation of the EDWARD Readout in 3FI65P1                            | 70 |

|   |      | 3.6.4  | Configuration and Testability Infrastructure                               | 72 |

|   |     | 3.6.5   | Peripheral Circuitry and Support Blocks                                      | 7  | 3 |

|---|-----|---------|------------------------------------------------------------------------------|----|---|

|   | 3.7 |         | ARD65P1 chip                                                                 |    |   |

|   |     | 3.7.1   | Motivation                                                                   |    |   |

|   |     | 3.7.2   | Architecture Overview                                                        |    |   |

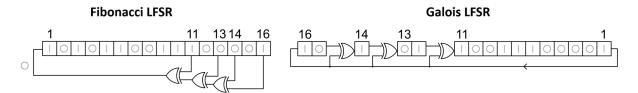

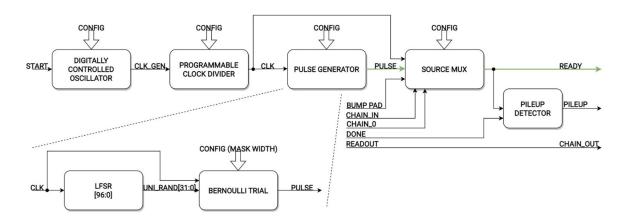

|   |     | 3.7.3   | Poisson-Distribution Event Generator                                         |    |   |

|   |     |         |                                                                              |    |   |

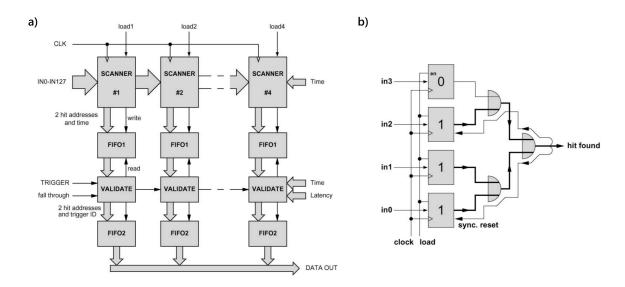

| 4 | Sim | ulation | and Performance Evaluation: Digital and Mixed-Signal Analyses                | 8  | 7 |

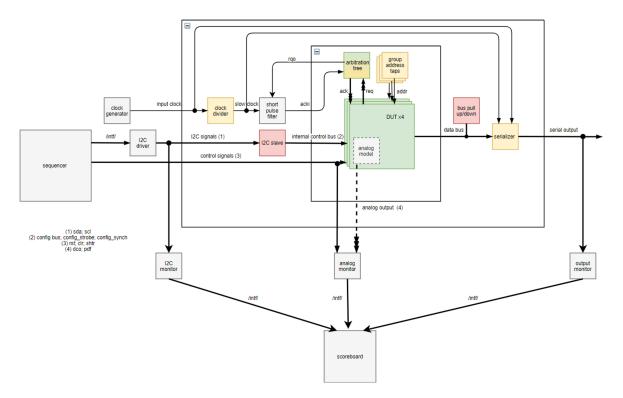

|   | 4.1 | Digita  | al Testbench Architecture Overview                                           | 8  | 7 |

|   | 4.2 | Digita  | al Test Campaign: RTL and Signoff Verification                               | 9  | 1 |

|   |     | 4.2.1   | Global Control Signals                                                       | 9  | 1 |

|   |     | 4.2.2   | Configuration Parameters                                                     | 9  | 2 |

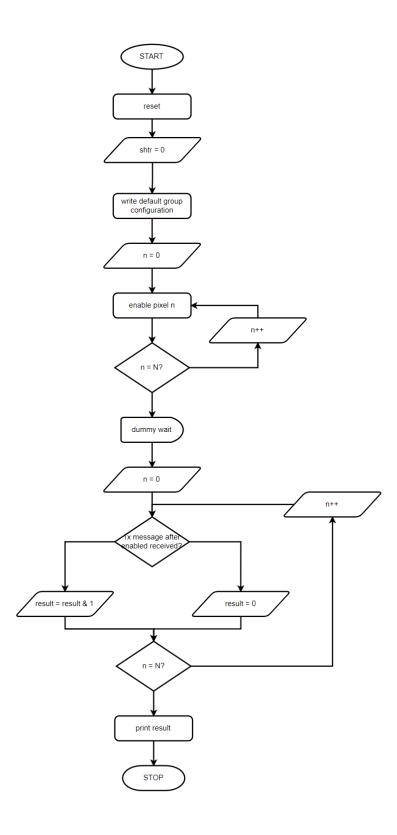

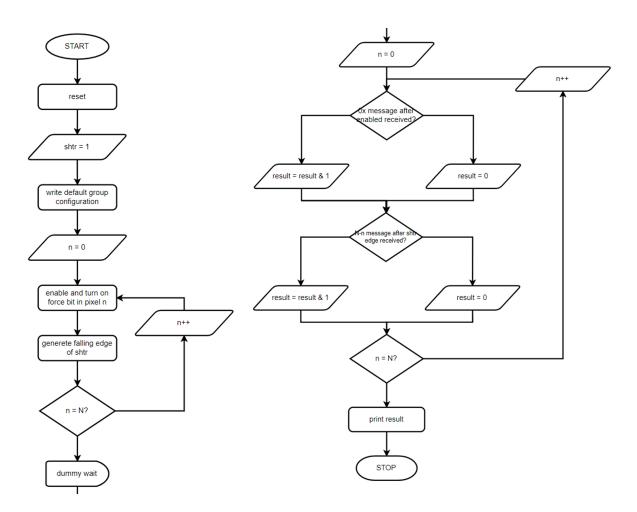

|   |     | 4.2.3   | Enable Test                                                                  | 9  | 3 |

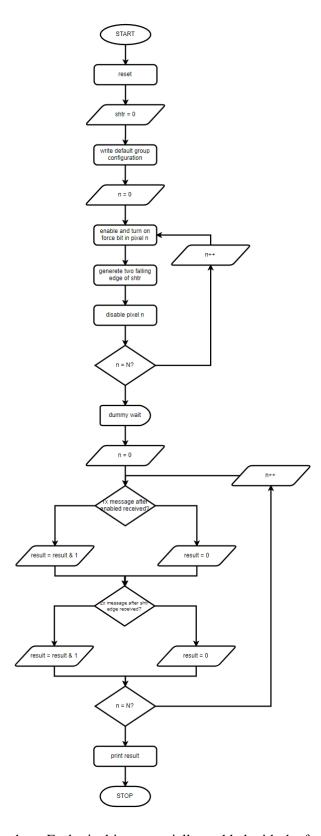

|   |     | 4.2.4   | Force Test v1                                                                | 9  | 3 |

|   |     | 4.2.5   | Force Test v2                                                                | 9  | 5 |

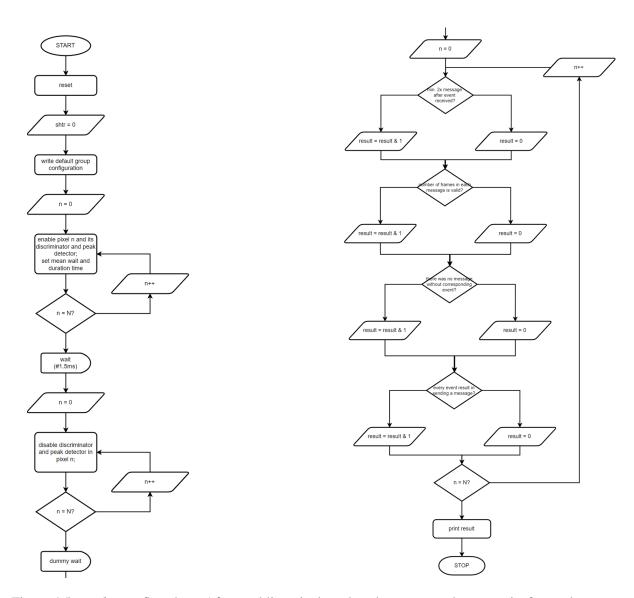

|   |     | 4.2.6   | Mode Test                                                                    | 9  | 8 |

|   |     | 4.2.7   | Testability Test                                                             | 9  | 8 |

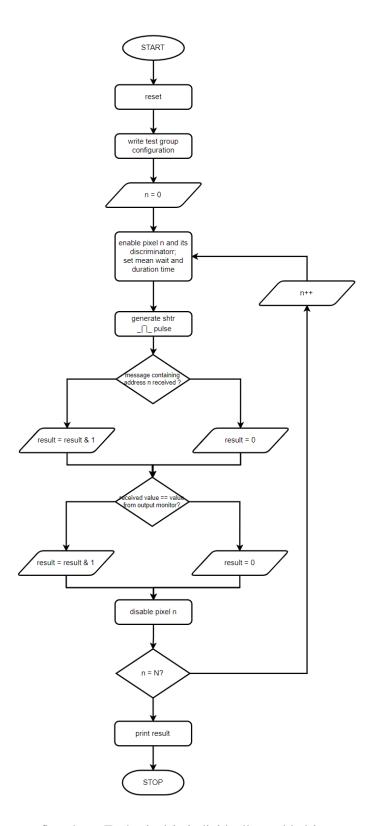

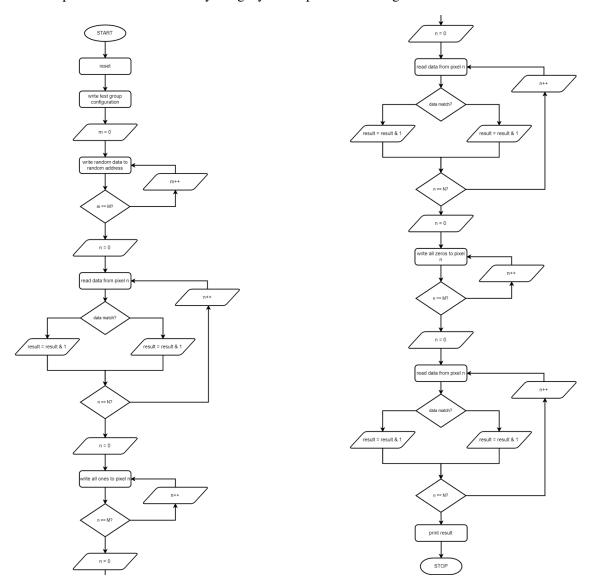

|   |     | 4.2.8   | Memory Test                                                                  | 10 | 0 |

|   |     | 4.2.9   | Summary of Digital Functional Verification                                   | 10 | 2 |

|   | 4.3 | Mixed   | d-Signal Timing Evaluation of a Single Readout Group                         | 10 | 3 |

|   |     | 4.3.1   | Simulation Setup and Objectives                                              | 10 | 3 |

|   |     | 4.3.2   | Key Timing Metrics                                                           | 10 | 3 |

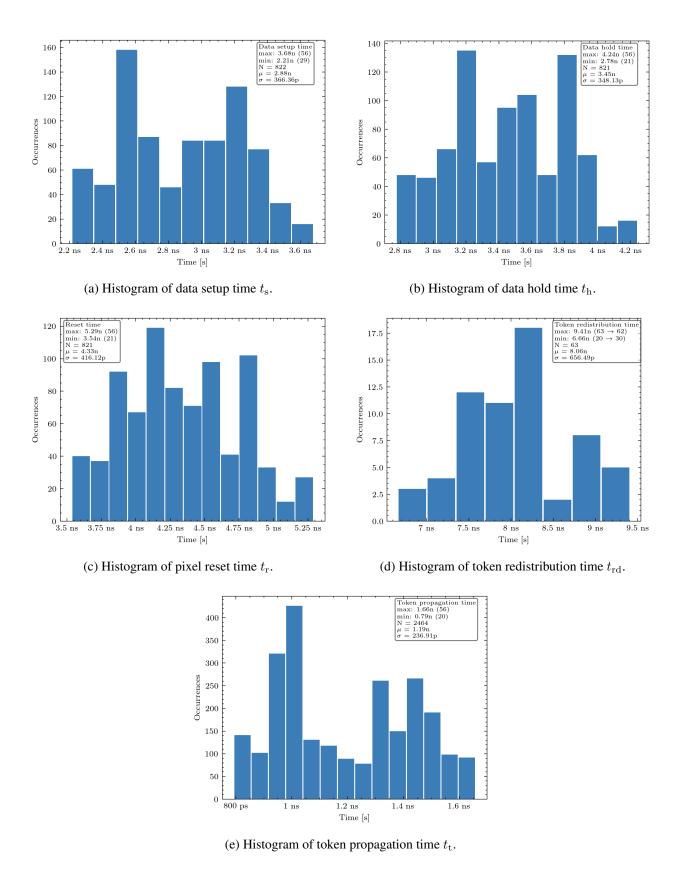

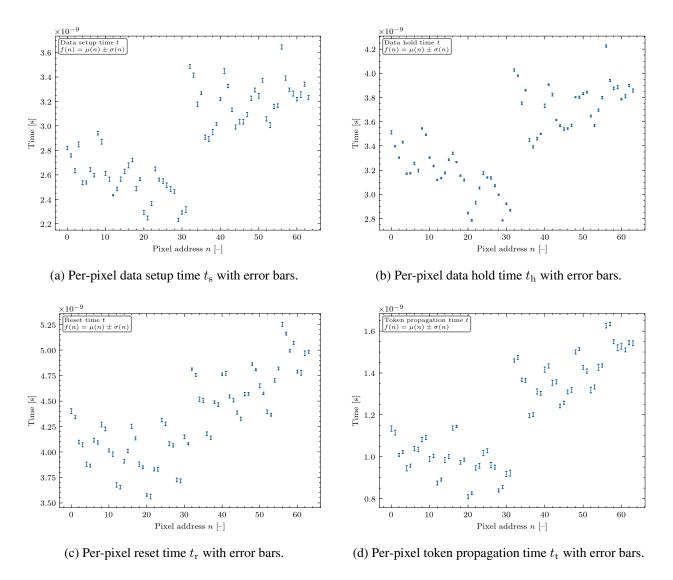

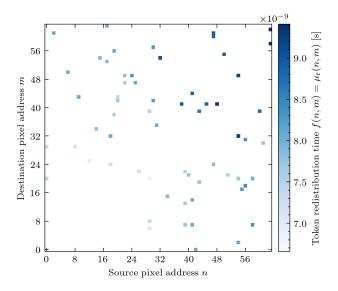

|   |     | 4.3.3   | Measured Timing Distributions and Spatial Variability                        | 10 | 4 |

|   |     | 4.3.4   | Summary of Mixed-Signal Timing Evaluation                                    | 10 | 8 |

|   | 4.4 | Analo   | og and Mixed-Signal Simulation of EDWARD65P1 and In-Pixel Event Generator    | 10 | 8 |

|   |     | 4.4.1   | Analog Simulation of In-Pixel Clock Generator                                | 10 | 9 |

|   |     | 4.4.2   | Digital Verification of Poisson-Based Signal Generator                       | 11 | 0 |

|   |     | 4.4.3   | Digital Simulation with Variable Event Rates and Queueing Model Comparison . | 11 | 1 |

| _ | _   |         |                                                                              |    | _ |

| 5 | _   |         | tal Validation                                                               | 12 |   |

|   | 5.1 |         | duction and Objectives                                                       |    |   |

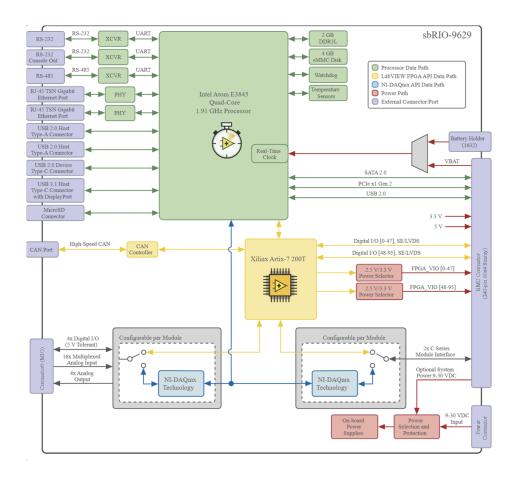

|   | 5.2 | •       | rimental Setup                                                               |    |   |

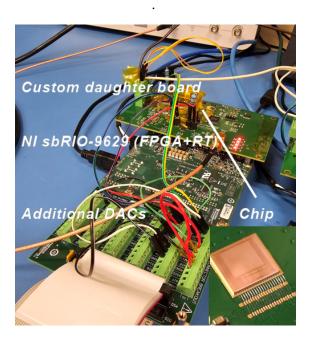

|   |     | 5.2.1   | ASIC Characterization Platforms                                              |    |   |

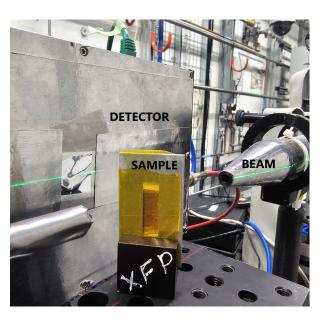

|   |     | 5.2.2   | Synchrotron Measurement at NSLS-II                                           |    |   |

|   |     | 5.2.3   | Configuration and Control Methodology                                        |    |   |

|   | 5.3 |         | lts: 3FI65P1 Experimental Testing                                            |    |   |

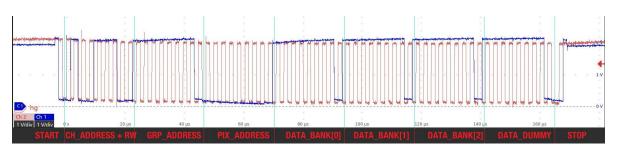

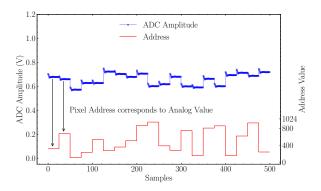

|   |     | 5.3.1   | Readout-Mode Verification of the 3FI65P1 Prototype                           |    |   |

|   |     | 5.3.2   | Preliminary Synchrotron Beamline Results                                     |    |   |

|   | 5.4 |         | Its: EDWARD65P1 Performance Validation                                       |    |   |

|   |     | 5.4.1   | Clock Generator Characterization                                             | 12 | 7 |

|   |     | 5.4.2   | Readout and Generator Characterization                                       | 12 | 8 |

| 6   | Conc    | Conclusion 1                                             |     |  |  |  |

|-----|---------|----------------------------------------------------------|-----|--|--|--|

|     | 6.1     | Restatement of Research Purpose                          | 133 |  |  |  |

|     | 6.2     | Integrated Discussion of Research Questions and Outcomes | 133 |  |  |  |

|     | 6.3     | Key Contributions and Scientific Significance            | 137 |  |  |  |

|     | 6.4     | Limitations and Challenges                               | 139 |  |  |  |

|     | 6.5     | Broader Implications and Recommendations                 | 141 |  |  |  |

|     | 6.6     | Directions for Future Work                               | 142 |  |  |  |

|     | 6.7     | Final Reflections                                        | 144 |  |  |  |

| Bil | bliogra | aphy                                                     | 147 |  |  |  |

# **List of Figures**

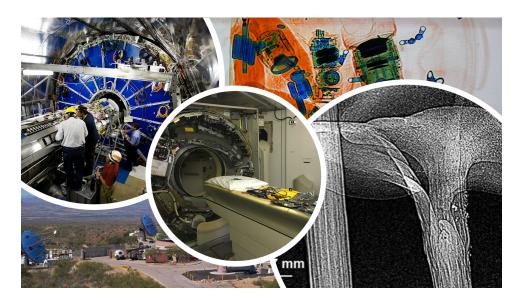

| 1.1  | Diverse industry applications of radiation-detection technology                               | 2  |

|------|-----------------------------------------------------------------------------------------------|----|

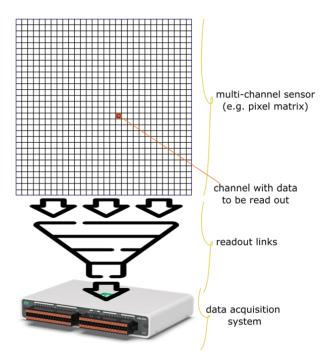

| 1.2  | Example of pixel detector X-Ray Camera                                                        | 3  |

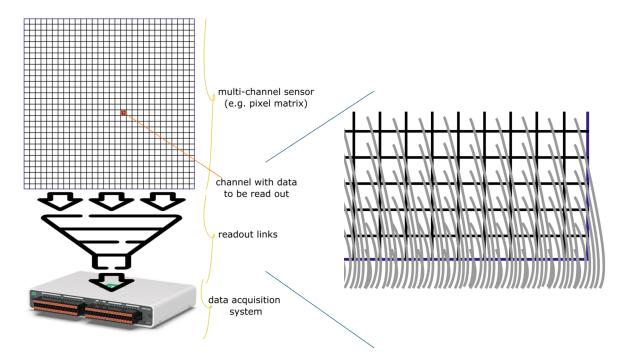

| 1.3  | Simplified schematic of pixelated detector readout structure                                  | 5  |

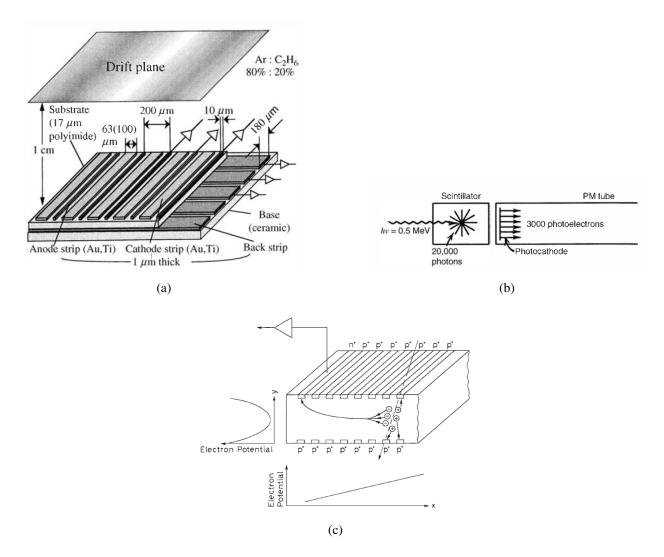

| 2.1  | Examples of different radiation detector implementations: (a) a gaseous detector, (b) a scin- |    |

|      | tillation detector, (c) a semiconductor detector                                              | 15 |

| 2.2  | Structure of a hybrid detector                                                                | 19 |

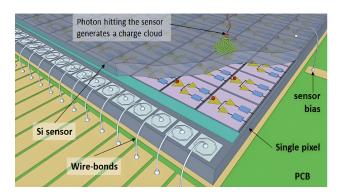

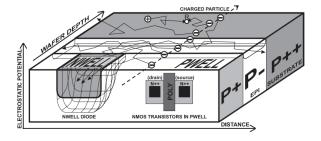

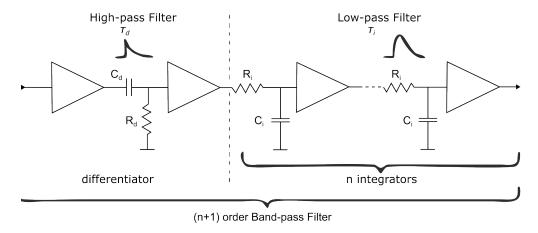

| 2.3  | Structure of MAPS detector                                                                    | 21 |

| 2.4  | Structural cross-section of a pixel in (a) a standard process MAPS and (b) a modern MAPS.     | 22 |

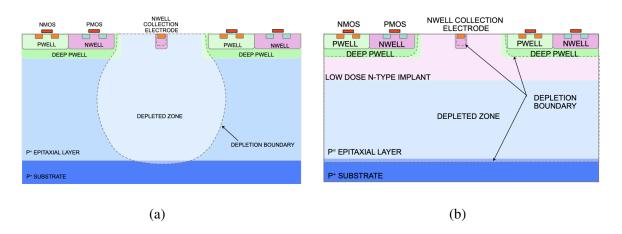

| 2.5  | Example of in-situ signal processing chain based on chip HEXID65P1                            | 25 |

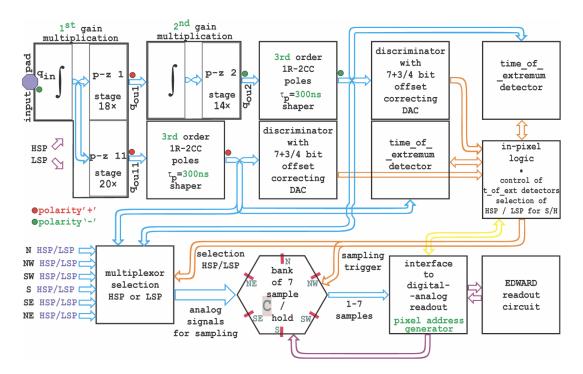

| 2.6  | $CR\text{-}RC^n$ pulse shaper                                                                 | 26 |

| 2.7  | General structure of a direct link readout architecture                                       | 30 |

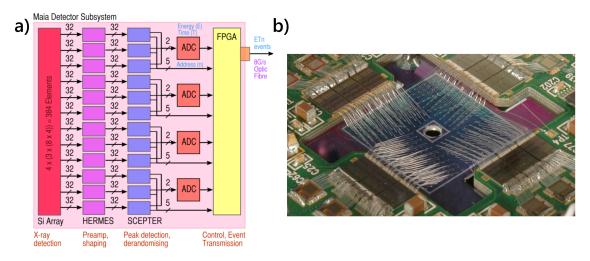

| 2.8  | Maia X-ray Microprobe Detector Array System                                                   | 30 |

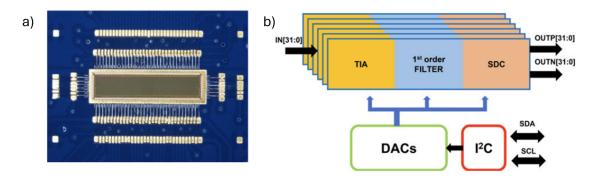

| 2.9  | Block diagram and microphotograph of AVG3_Dev ASIC                                            | 31 |

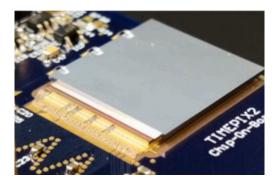

| 2.10 | Timepix2 chip                                                                                 | 31 |

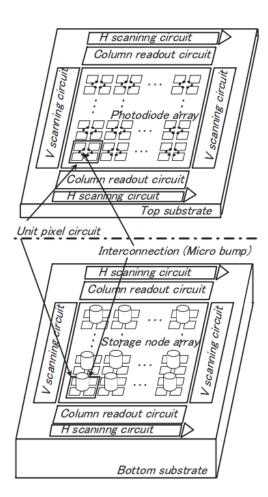

| 2.11 | 3D-stacked CMOS image sensor architecture with global and rolling shutter modes               | 32 |

| 2.12 | Polling-based token passing scheme, as used in VIP2a                                          | 33 |

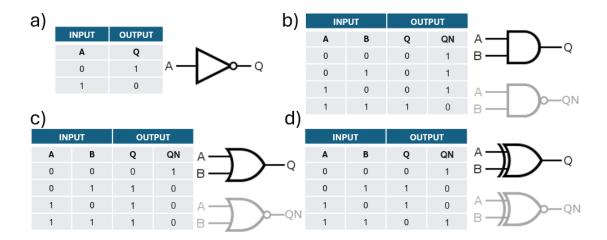

| 2.13 | Basic combinational logic gates: (a) inverter, (b) AND/NAND, (c) OR/NOR, (d) XOR/XNOR.        | 37 |

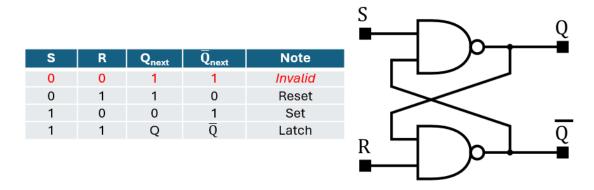

| 2.14 | RS latch: a fundamental asynchronous sequential element, constructed from cross-coupled       |    |

|      | NAND or NOR gates                                                                             | 37 |

| 2.15 | Comparison of synchronous and asynchronous logic paradigms                                    | 37 |

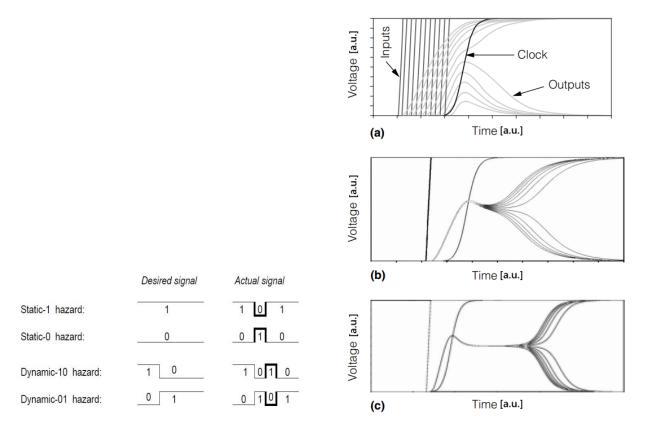

| 2.16 | Different types of logic hazards in digital circuits                                          | 38 |

| 2.17 | Simulated latch metastability under increasingly fine input timing shift                      | 38 |

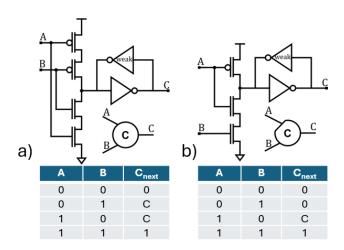

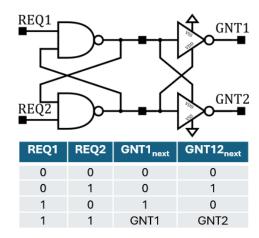

| 2.18 | Symmetric and asymmetric C-element implementations for asynchronous synchronization           | 39 |

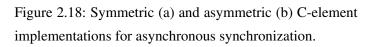

| 2.19 | Arbiter circuit together with metastability filter used for asynchronous priority resolution  | 39 |

| 2.20 | Conceptual diagram of AER communication                                                       | 41 |

| 2.21 | The MEPHISTO architecture.                                                                    | 42 |

| 2.22 | General structure overview of ALPIDE chip                                                     | 43 |

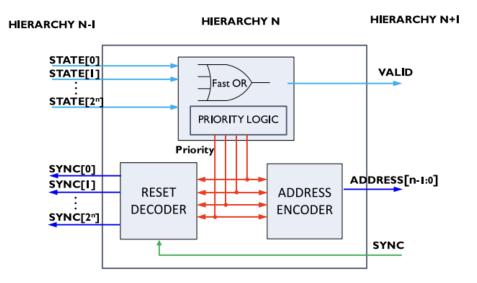

| 2.23 | Basic logic block of the AERD system: priority logic, address encoder, and reset decoder      | 44 |

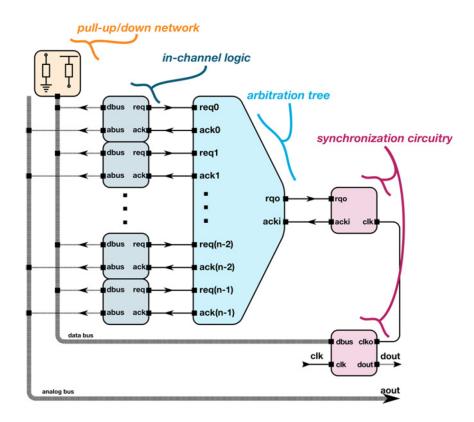

| 3.1  | EDWARD architecture block diagram                                                             | 46 |

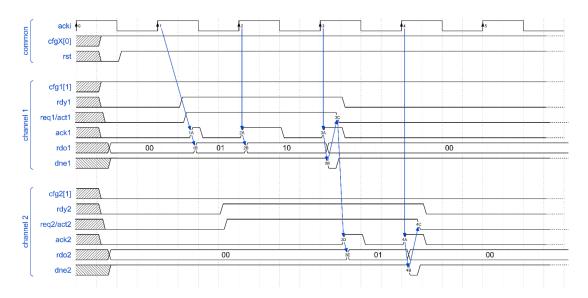

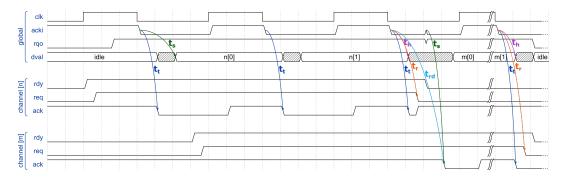

| 3.2  | Timing diagram of a multi-phase in-channel readout                                            | 48 |

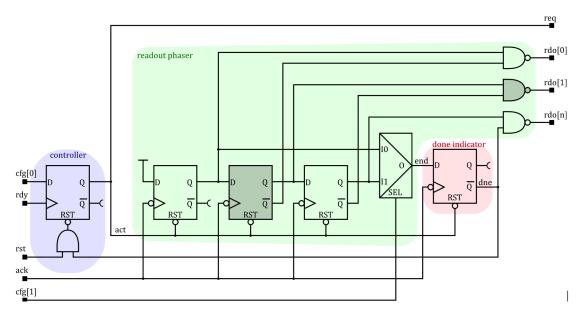

| 3 3  | In-channel logic structure including the controller readout phaser, and done indicator        | 49 |

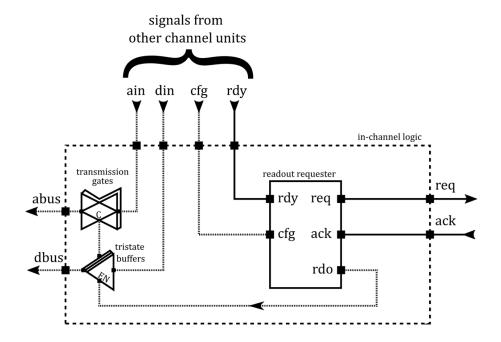

| Simplified schematic of shared bus interfaces                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

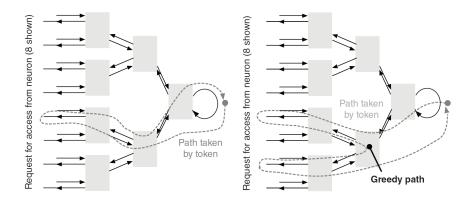

| Difference between non-greedy/fair arbitration and greedy/unfair arbitration                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

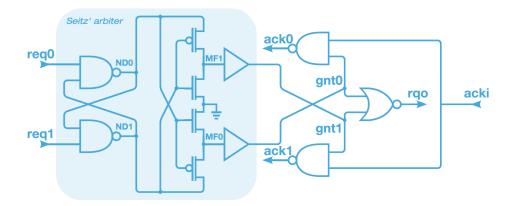

| Structure of arbitration cell Type 0 using Seitz arbiter                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

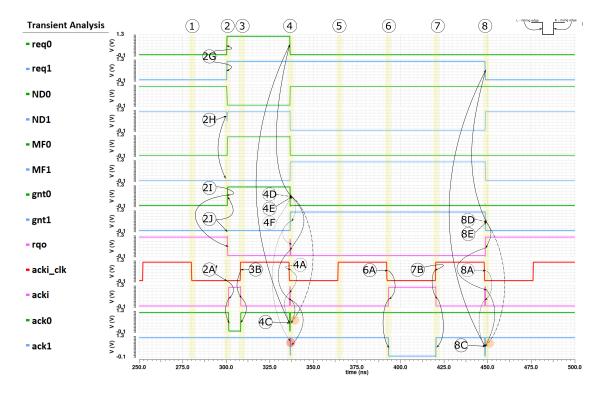

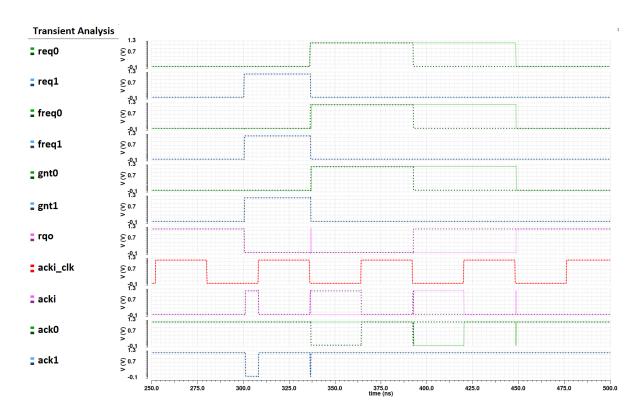

| Waveforms showing arbitration cell Type 0 behavior under simultaneous requests               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Structure of arbitration cell Type II                                                        | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

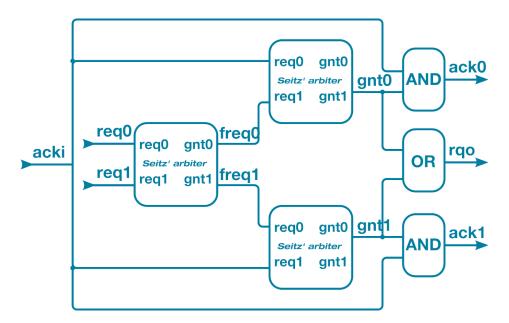

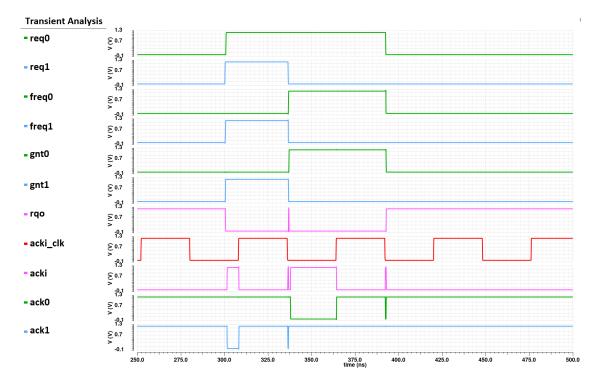

| Waveforms from a tree composed entirely of Type II arbitration cells                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Structure of arbitration cell Type I with fairness-enhancing logic                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Waveforms showing the operation of arbitration cell Type I when only two neighboring         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| channels request readout                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

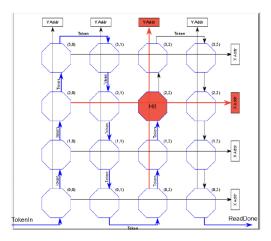

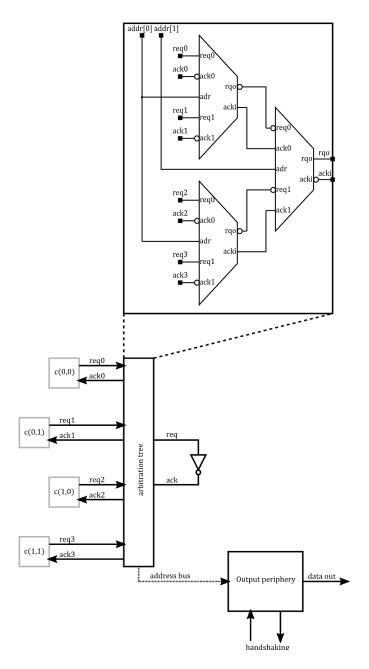

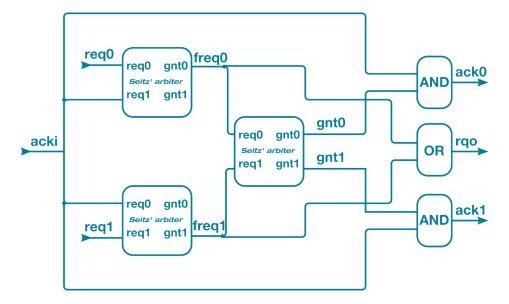

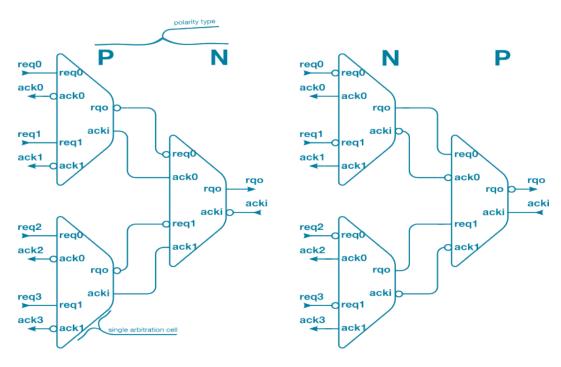

| Examples of NP and PN stage connections in the arbitration tree                              | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

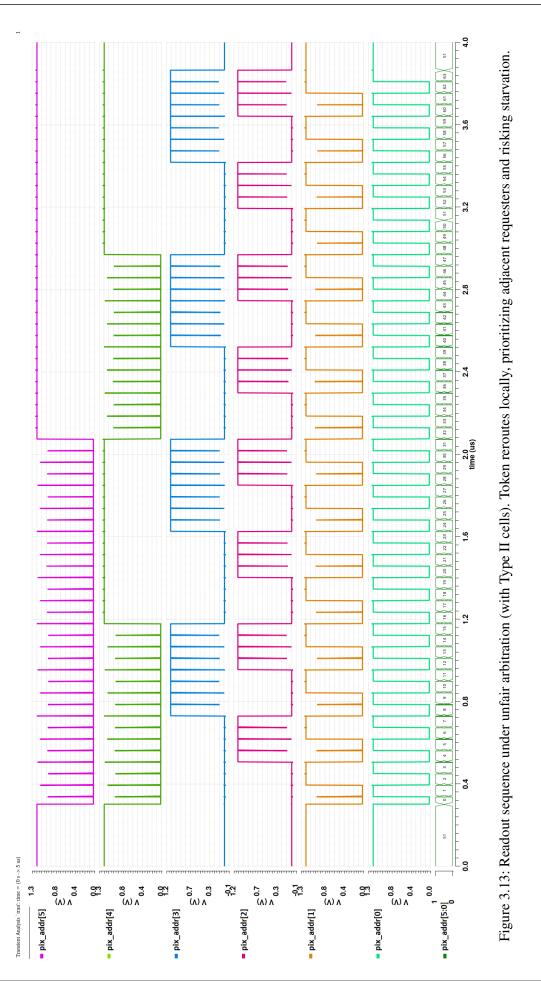

| Readout sequence under unfair arbitration (with Type II cells)                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

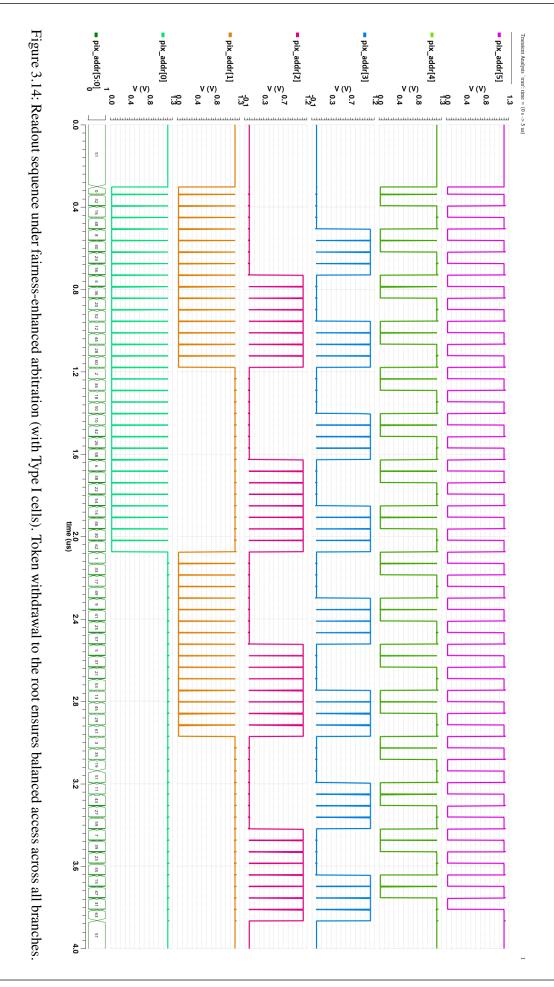

| Readout sequence under fairness-enhanced arbitration (with Type I cells)                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

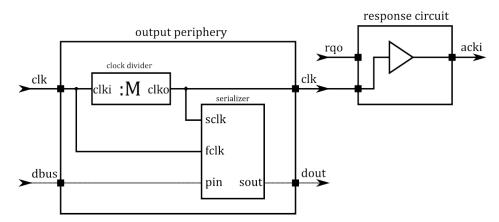

| Peripheral synchronization block                                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

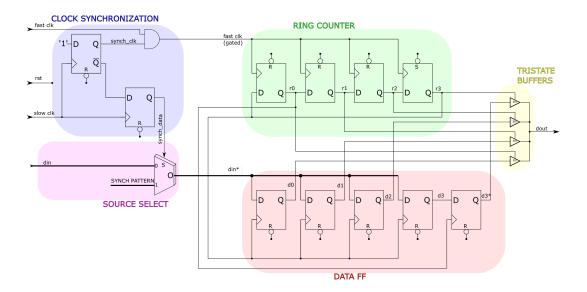

| Conceptual serializer architecture compatible with EDWARD                                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

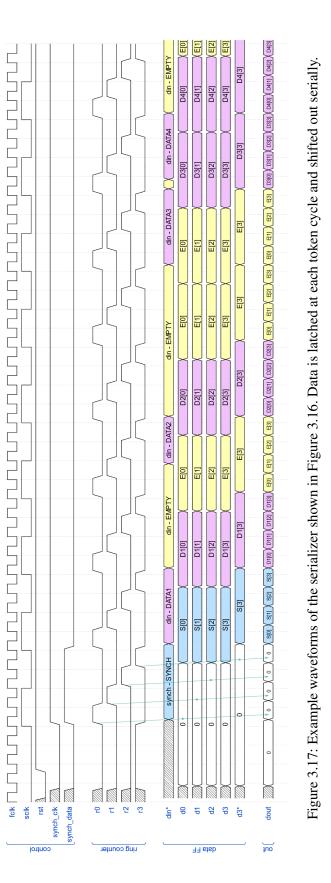

| Example waveforms of the serializer shown in Figure 3.16                                     | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

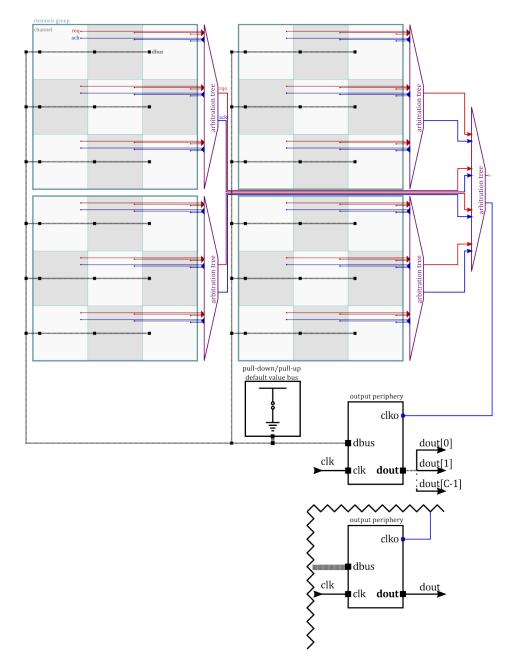

| Sub-array grouping with a spatially distributed arbitration tree and a common serializer     | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

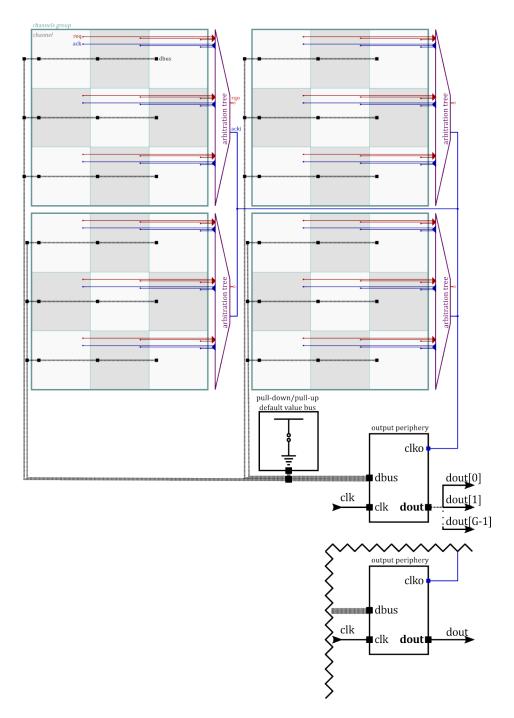

| Architecture with independent arbitration trees and separate output paths for each group     | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Illustration of the full-field fluorescence imaging concept, where the sample is illuminated |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| uniformly and the detector records the spatial and spectral content of the emitted $X$ -rays | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

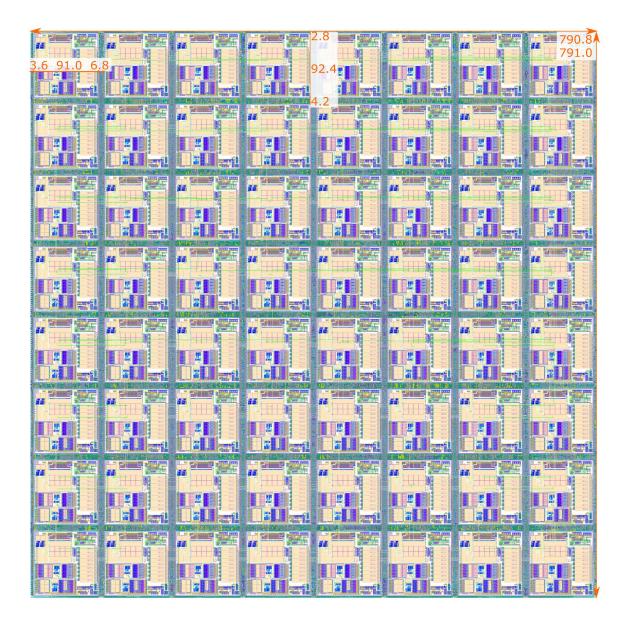

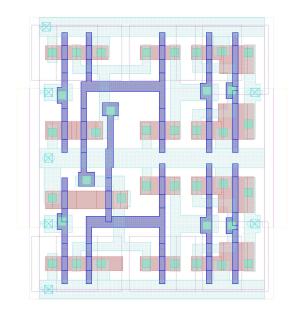

| Layout of a single $8 \times 8$ pixel group                                                  | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |